산화막 용도

1. 소자간 격리 - LOCOS, STI

- 소자가 점점 작아짐에 따라 소자 간 전류가 누출되는 것을 막기 위해 소자 사이에 산화막을 넣어 누출을 방지한다.

- 과거에는 LOCOS(Local Oxidation of Silicon)를 많이 사용했지만 Bird's Beak 현상 발생으로 최근에는 STI(Shallow Trench Isolation) 방식을 많이 사용하고 있는 추세이다.

LOCOS

Bird's Beak 현상 : 열성장 속도 차이 때문에 노출된 부분의 가장자리는 조금 성장하고, 노출된 부분의 중심부는 많이 성장하여 새부리 모양의 불균형한 모습이 발생하는 현상을 말한다.

해당 이미지로 설명하자면

a) Silicon Nitride를 부착하기 위해 실리콘 웨이퍼에 Pad Oxide를 형성하고, 그 위에 Silicon Nitride를 부착한다.

* Silicon Nitride : Silicon Dioxide보다 더 견고한 물질로, 원하는 산화막 형성을 위해 사용된다.

b) Silicon Nitride가 부착된 부분은 상대적으로 산화가 덜 일어나게 되고, Silicon Nitride가 없는 오픈된 부분은 산화가 더 두껍게 진행된다.

c) 마지막으로 Silicon Nitride를 제거하면 최종 산화막이 형성된다.

LOCOS방법은 Bird's Beak 현상으로 인해 산화막을 직각형태로 깔끔하게 혀성하기 어렵다 따라서 현재는 LOCOS 방법을 잘 사용하지 않는다.

STI

해당 이미지로 설명하자면

a) 실리콘 웨이퍼에 Nitride와 Resist를 부착하고 홈(구멍)을 만든다.

b) Pad oxide를 약간 제거하는 과정을 거친다.

c) 다시 산화를 진행해 Oxide를 올리면 Liner Oxide가 완성된다.

d) 다시 산화를 진행해 Oxide를 다시 한번 더 진행해 Isolat Oxide를 완성한다.

e) CMP로 Isolat Oxide의 윗부분을 제거한다.

* CMP(Chemical Mechanical Polishing) : 화학적 기계 연마

f) Nitride를 제거하면 최종 산화막 구조가 완성된다.

STI는 공정 단계가 복잡해졌지만 Bird's Beak 문제를 해결했다.

2. Gate Insulator

- Gate Oxide는 MOSFET에서 Gate Insulator로 사용된다. 얇고 특성이 좋아야 하기 때문에 Dry Oxidation 건식산화로 제작한다.

- Gate Insulator은 절연층으로 사용되어 MOSFET 소자의 게이트 전극과 채널을 분리하고, 게이트 전극에 인가되는 전압을 채널로 전달한다. 이 과정에서 게이트 전극과 채널 사이에 생기는 전기장으로 인해 채널 전하의 분포가 변화하게 되어 소자의 작동 상태가 결정된다. 따라서 Gate Insulator은 소자의 전기적 특성을 결정하고, 전하를 차단하는 역할을 한다.

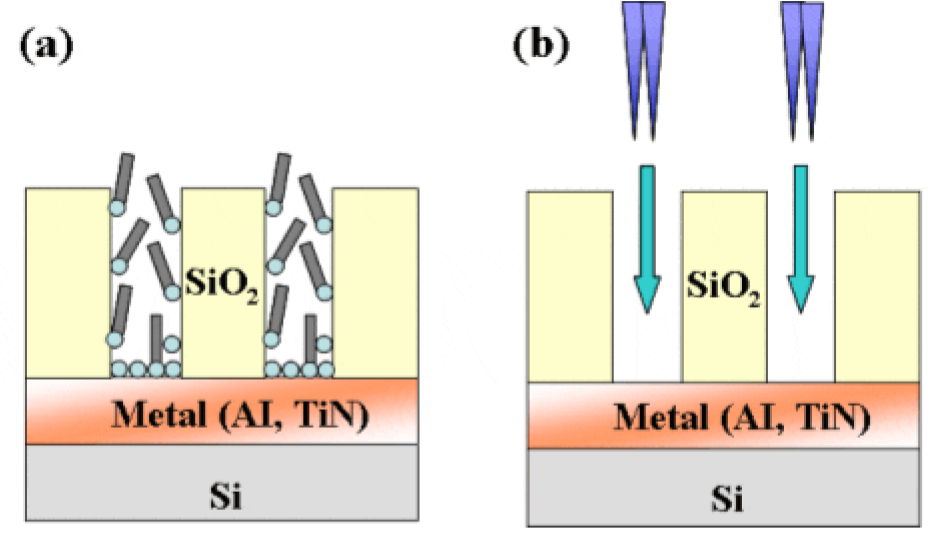

3. ILD, IMD

ILD(Inter Layer Dielectrics) : 소자와 커패시터가 형성된 층위에 주로 쓰이므로 형성되고 난 후 막의 평탄도가 높아야 한다.

- Metal-Silicon 사이의 절연을 담당한다.

- Contact간의 절연을 담당한다.

- 지지대 역할을 담당한다.

IMD(Inter Metal Dielectrics) : 층간 간섭을 막기 위해 커패시턴스를 낮춰야 한다. 때문에 IMD막은 차폐성이 좋은 저유전 물질을 주로 사용한다.

- Metal-Metal 사의이 절연을 담당한다.

- Metal-Via 사이의 절연을 담당한다.

- 지지대 역할을 담당한다.

4. Mask Layer

- Mask Layer은 소자의 원하는 패턴을 형성하는 데 사용한다. 이를 위해 노광, 이온 주입 공정 등에서 마스크로 사용되어 패턴을 형성한다.

- 또한 소자의 미세한 구조를 만들기 위해 회로 배치, 연결 패턴 등에서도 사용된다. 이러한 작업에서는 마스크 레이어의 정밀한 제어와 고도의 정확성이 요구된다.

'취업 > 반도체 이론 정리' 카테고리의 다른 글

| 산화막 생성 방법 (산화공정) (0) | 2023.02.28 |

|---|---|

| 반도체 산화공정 (Oxidation) (0) | 2023.02.28 |

| 웨이퍼 제조 공정 (0) | 2023.02.27 |

| 실리콘 다결정 성장 방법 (0) | 2023.02.27 |

| 실리콘 단결정 성장 방법 (0) | 2023.02.27 |

댓글