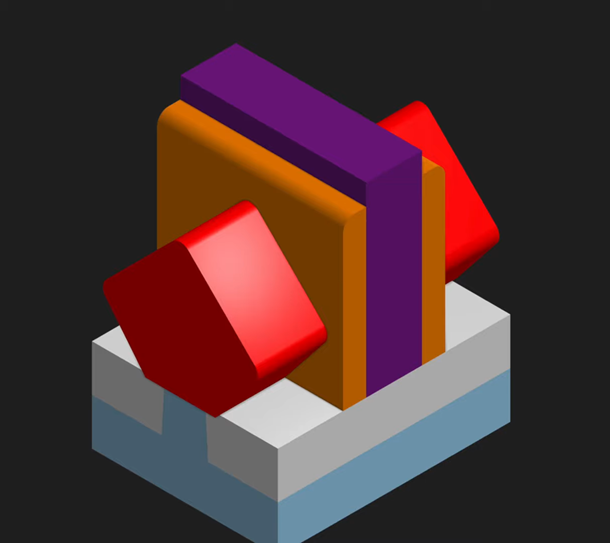

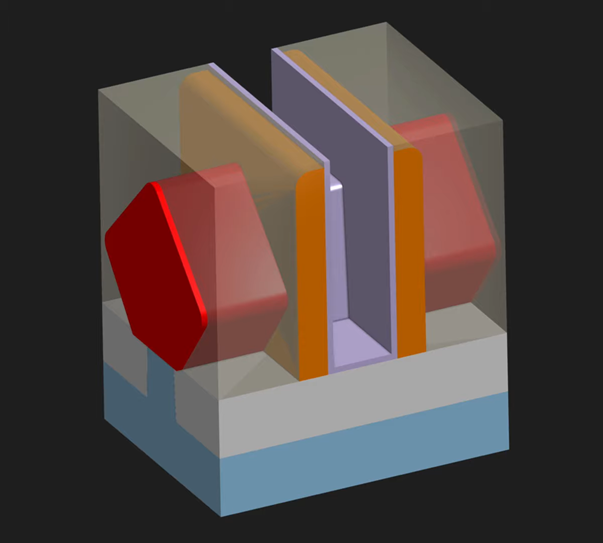

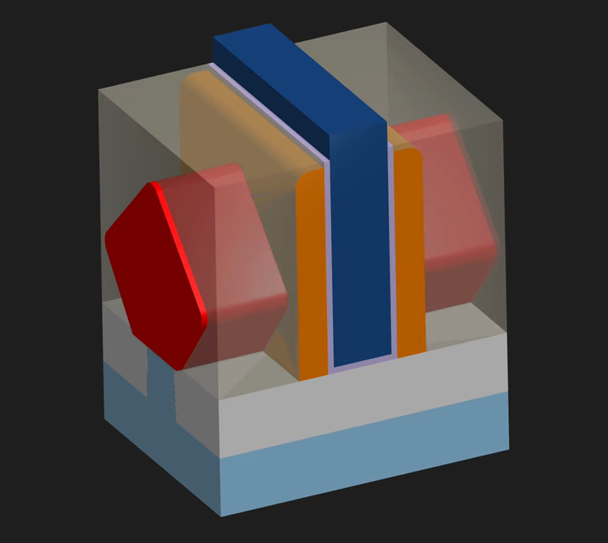

FinFET 구조

기존 Planar 구조의 한계를 극복하기 위해 도입된 입체 구조의 공정기술로, GATE와 Channel 사이의 접점을 키워 반도체 성능 향상 및 누설전류 감소를 이뤄낸 구조이다.

* 삼성전자는 14nm 기술부터 FinFET구조를 활용했다. 4nm까지 핀펫 구조를 활용하였으며, 현재는 GAA와 MBCFET으로 한계를 극복하고 있다.

FinFET 구조가 도입된 이유

칩의 집적도가 나노단위까지 미세화됨으로서 벽(Insulator)이 있어도 전자가 통과하는 터널링효과(Turnneling Effect)가 발생했다. 이는 트랜지스터의 누설전류를 증가시켰고 칩 성능에 악영향을 미쳤다. 이런 문제점을 해결하기 위해 FinFET구조가 도입되었다.

FinFET 구조 도입으로 디지털 회로에서는 누설전류의 감소로 인한 저전력의 구현이 가능해지고, 아날로그 회로에서도 같은 Channel의 길이를 가지는 Planar MOSFET보다 더 많은 구동전류를 확보할 수 있어 고속으로 동작하는 회로가 구현이 가능해졌다.

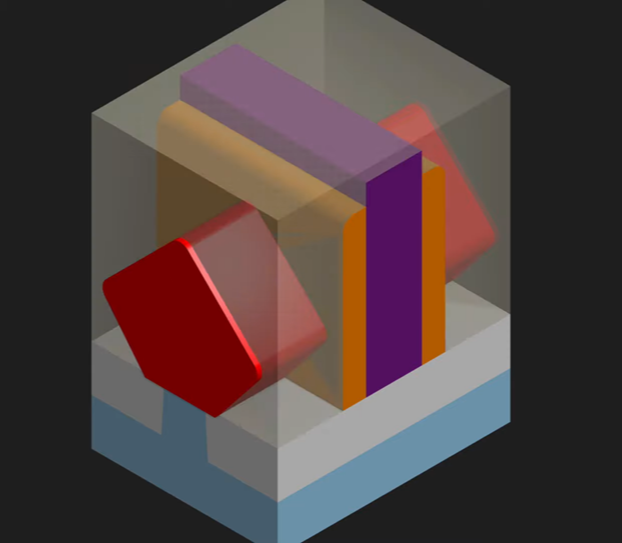

FinFET Process

1. Hardmask deposition

기존의 PR은 종횡비(Aspect Ratio)가 상대적으로 낮다. 이를 해결하기 위해 얇은 PR을 사용할 수 있으나, 이후 식각공정에서 견디지 못하기 때문에 Hardmask를 도입했다.

* 위 그림에서 초록색 부분 (SiN)

2. Fin patterning

Hardmask를 기반으로 기판을 패터닝한다.

3. STI-dielectric deposition

Fin을 서로 분리하기 위해 STI-dielectric를 증착한다. STI(Shallow Trench Isolation)은 절연 특성이 좋아 각 소자를 분리시키고 Leakage Current를 줄인다.

4. Etchback (STI)

기판에 증착 후 전면을 포토 공정 없이 다시 etching 하는 공정이다. 전류를 차단하는 Insulator인 Spacer 제작에 사용된다.

5. Dummy gate formation

Gate-Last 공정이다. Spacer와 S/D(Source/Drain)을 먼저 형성하기 위해 dummy gate를 형성한다.

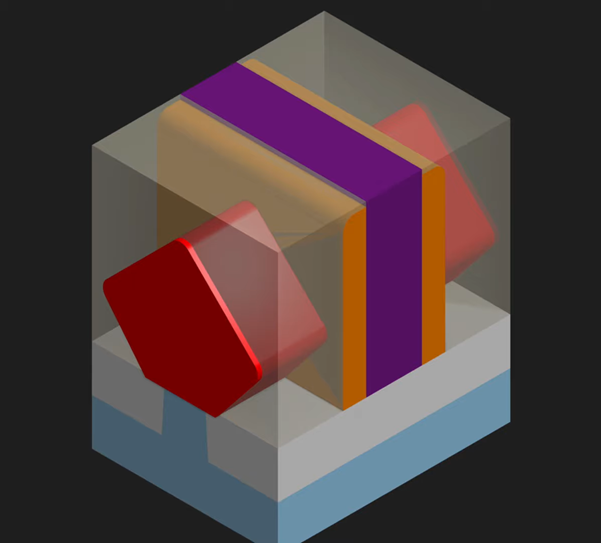

6. Spacer formation

S/D 사이에서 발생되는 Hot Carrier Injection으로부터 gate를 보호하기 위한 절연막을 형성한다. Etchback 공정에서 etching 되지 못한 일부 폴리실리콘이 gate 주위에 남게 된다.

7. S/D epitaxy

실리콘 결정 방향에 따라 epitaxy 성장 속도가 다르므로 다이아몬드 형태로 성장하게 된다.

Si, SiGe를 주로 사용한다. 특히 SiGe은 채널에 Compressive Stress를 가하여 hole mobility를 증가시킬 수 있는 이점이 있어 주로 사용된다.

* epitaxy : Seed 웨이퍼를 밑에 깔고 격자 방향을 유지하면서 단결정(한 종류로 된 결정 전체가 일정한 결정축을 따라 규칙적으로 생성된 고체)으로 성장해 추가로 새로운 층을 쌓아 올린다는 의미이다.

8. ILD0 deposition

소자와 커패시터가 형성된 층 위에 ILD(Inter Layer Deposition) 층간절연막을 증착해 형성한다. 이때 막의 평탄도가 중요하다.

9. CMP

Dummy gate 노출을 위해 ILD를 CMP로 깎는다.

Slurry를 이용하여 표면을 평평하게 만든다. CMP의 etch stop layer로 Silicon Nitride를 사용한다.

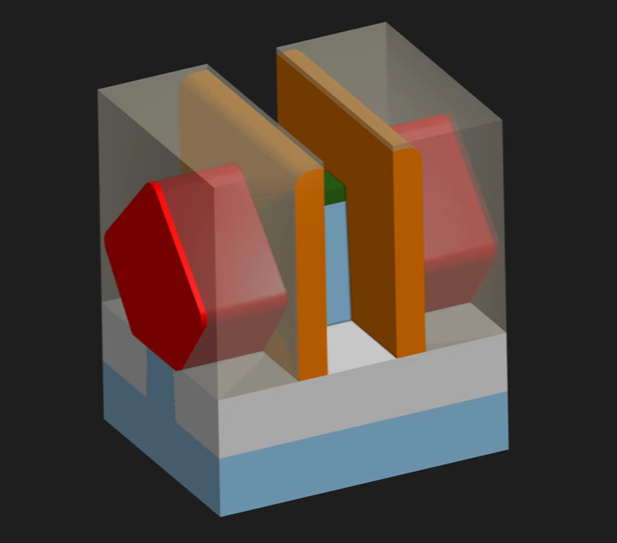

10. Dummy gate removal

Dummy gate 제거를 통해 fin 노출한다.

11. Gate dielectric deposition

High-K dielectric 증착한다.

12. Gate stack formation

Metal의 work function, bandgap을 고려하여 여러 종류의 metal이 쌓인 gate를 형성한다.

댓글