반응형

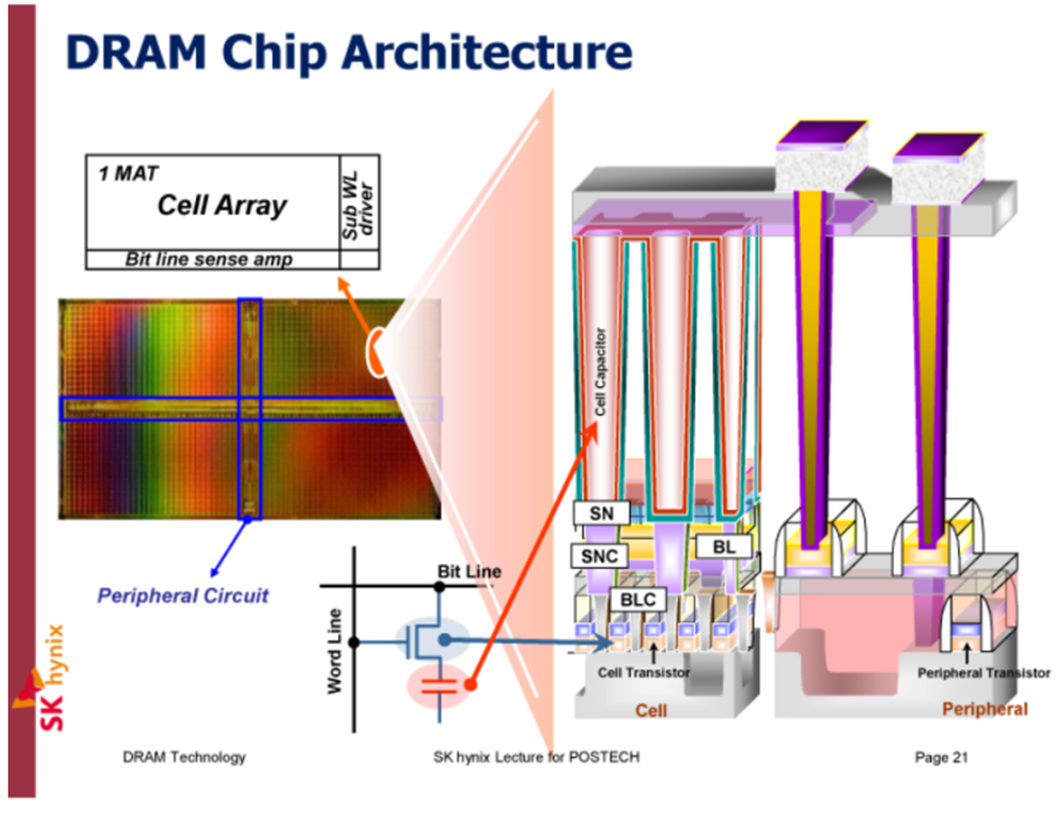

DRAM(Dynamic Random-Access Memory)

- 정보를 구성하는 개개의 bit를 축전기에 저장하는 기억 장치

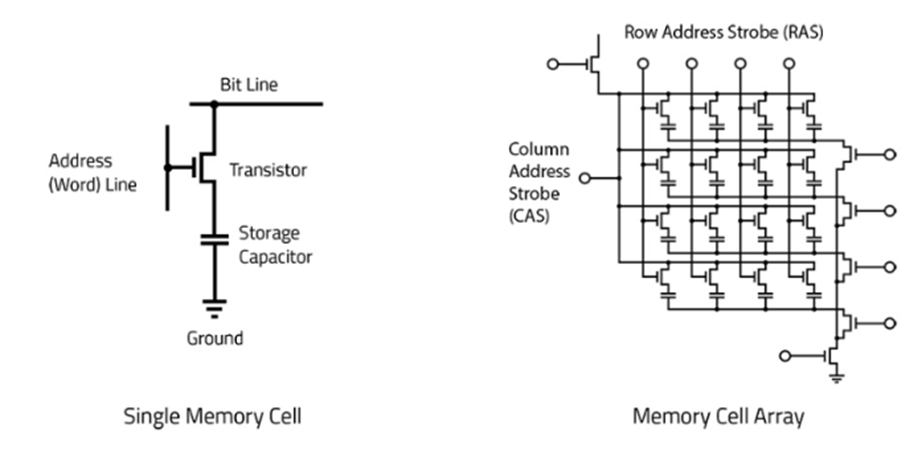

- DRAM의 구조는 1 transistor + 1 capacitor + Word line + Bit line

- 회로 구조가 단순하여 동작속도가 빠름

- 휘발성 메모리이며 refresh 해야만 기억된 정보 유지 가능

word line : 트랜지스터 게이트 전극에 연결된 도선으로 트랜지스터 on, off를 명령하여 커패시터에 접근 여부를 결정한다.

bit line : 커패시터에 저장된/저장될 데이터를 읽고 쓰는 역할이다. 소스(드레인)에 연결된 도선으로 커패시터에 저장된/저장될 데이터를 읽고 쓰는 역할을 수행한다.

DRAM 작동 방식

Write

1.WL(Word Line)을 ON 한다.

2.데이터 '1'의 경우에는 BL에 전압(Vhigh/Vdd)을 인가, 데이터 '0'의 경우에는 BL에 전압(Vlow/GND)을 인가하면 커패시터에 전하가 각각 충전, 방전된다.

3.이후 WL을 'OFF' 시키면 저장된 데이터를 기억하고 있는 상태가 된다.

Read

1.WL을 'ON'시키면 커패시터와 BL이 연결되어 커패시터의 전하를 BL과 공유하게 된다.

2.커패시터가 충전되어 있으면 BL전압이 미세하게 증가하고, 방전되어 있으면 BL전압이 미세하게 떨어진다.

3.이러한 미세한 전압 변화를 증폭하여 데이터 '1','0'을 각각 읽게 된다.

Refresh

•커패시터의 특성상 전하를 저장할 수 있는 시간이 매우 짧아서 금방 방전된다. 따라서 DRAM은 평소에 데이터를 원복해주는 Refresh란 과정을 반복해 데이터 값을 유지시켜 주어야 한다.

•이때 Refresh 간격이 길수록 좋은데 이를 위해서는 저장된 전자의 양을 늘리고 저장된 전자가 누설되는 누설전류를 최소화해야한다. 그러나 커패시턴스를 무한정 올리면 저장시간/방전시간이 길어지므로 DRAM의 속도가 떨어지게된다.

•최근에는 미세화로 인해 충분한 커패시터 용량을 확보하기 점점 힘들어지고 있다.

•누설전류를 최소화하기 위해 Tr의 Vth를 크게 하거나 유효 채널 길이를 늘이는 RCAT(Recess Channel Array Transistor)를 사용한다.

반응형

'취업 > 반도체 이론 정리' 카테고리의 다른 글

| 포토 공정 기술(Multi Patterning, PSM, OPC, ARC) (0) | 2023.06.03 |

|---|---|

| SRAM이란? (구조 및 작동방식) (0) | 2023.06.03 |

| PPAC란? (0) | 2023.06.03 |

| [포토공정] 분해능과 초점심도 (0) | 2023.05.13 |

| [포토공정] 극자와선(EUV) 공정과 난이도 (2) | 2023.05.13 |

댓글